BTC/HKD+3.55%

BTC/HKD+3.55% ETH/HKD+4.21%

ETH/HKD+4.21% LTC/HKD+3.81%

LTC/HKD+3.81% ADA/HKD+4.79%

ADA/HKD+4.79% SOL/HKD+3.78%

SOL/HKD+3.78% XRP/HKD+3.39%

XRP/HKD+3.39%

作者|任源、潘俊、劉京京、何燕冬、何進

來源|《微納電子與智能制造》期刊

現代電子產品和設備在諸如通信、娛樂、安全和醫療保健等許多方面改善了我們的生活質量,這主要是因為現代微電子技術的發展極大地改變了人們的日常工作和互動方式。在過去幾十年中,摩爾定律一直是通過不斷縮小芯片上的器件特征尺寸來提高計算能力,帶來了電子產品諸如更高速度、更低成本和更小功耗等優勢。GordonMoore最初的觀察是芯片中的晶體管數量大約每2年增加1倍,DavidHouse進一步預測,由于更多更快的晶體管,芯片性能將每18個月翻一番。雖然GordonMoore的預測已經成功超過50年,但是今天的硅CMOS技術正在接近其尺寸的基本物理極限,摩爾定律的延續性已經變得越來越具有挑戰性。

這意味著電子產品和設備的性能增益不再僅僅依賴于器件特征尺寸的縮小,人們有必要發明新的IT技術或新的計算原理,以滿足應用對計算能力和低功耗等方面不斷增長的需求,而人工智能的出現為突破這種局限性提供了無限可能。人工智能(artificialintelligence,AI)指由人制造出來的機器來呈現人類智能的技術,而人工智能芯片指能夠運行人工智能技術和相關算法的半導體芯片。本文將對人工智能芯片的研究進展及市場發展進行介紹。

人工智能芯片的發展

據了解,人工智能(AI)技術的發展和應用在美國、中國和歐盟等世界主要國家中已經成為國家戰略,在國家的科技發展和產業競爭中占據越來越重要的位置。同時,AI技術在手寫識別(例如MNIST數據集)、人臉識別(例如Facebook的DeepFace)、語音識別(例如亞馬遜的Alexa、Apple的Siri、微軟的Cortana)、機器人技術(例如機器人操作系統)、自動駕駛(例如TartanRacing),甚至智力游戲(例如Google的AlphaGo)和視頻游戲(例如Pac-mAnt)等領域得到了廣泛應用。隨著人工智能的發展,產生了更多的專業技術,比如神經網絡模型、機器學習等,依靠經驗學習而不是編程來做出決策。反過來,機器學習為深度學習奠定了基礎,深度學習涉及分層算法,以便更好地理解數據。

自20世紀50年代開始,人類對人工智能技術的探索從來就沒有停止過。“人工智能”一詞是由科學家約翰·麥卡錫(JohnMcCarthy)、克勞德·香農(ClaudeShannon)和馬文·明斯基(MarvinMinsky)于1956年在達特茅斯會議上提出的,從此揭開人工智能研究的序幕。1962年Rosenblatt出版《神經動力學原理》及其1957年設計的模擬計算器,被視作深度神經網絡模型的算法原型。1969年,Minsky與Papert出版《感知器》,指出單層神經網絡訓練出來的圖像識別算法連對稱圖形都無法正確識別。

對于多層神經網絡,由于人造神經元的運算極限嚴重受限于當時計算機的算力不足,導致多層神經網絡也無法被當時和后來的計算機的芯片運算效能實現,這造成了人工神經網絡領域在1970年代的寒冬時期。

1982年,日本開始第五代計算機項目研究計劃,同時美國也投入不少資源在第五代計算機的研發中,但最終依然無法解決圖像和音訊識別的重大問題。1985年,Hinton與Sejnowski發表了之前被視為不可能實現的基于玻爾茲曼機的“多層神經網絡”,1986年,Rumelhart和Hinton發表“BP反向傳播算法”,1989年,貝爾實驗室成功利用反向傳播算法,在多層神經網絡開發了一個手寫郵編識別器。同年,Mead出版AnalogVLSIandNeuralSystems,開創了基于仿生芯片的神經形態工程領域。

1993年,YannLeCun的團隊使用DSP在一臺486電腦上實現深度學習算法,其作為推理芯片,已可辨識手寫的數字。至此,通用芯片CPU的算力大幅提升,但仍無法滿足多層神經網絡的計算能力需求。1994年,MichaelGschwind等使用FPGAs實現神經網絡的算法應用,1998年,YannLeCun和YoshuaBengio發表了手寫識別神經網絡和反向傳播優化相關的論文“Gradient-basedlearningappliedtodocumentrecognition”,開創了卷積神經網絡時代的到來。

2006年,Hinton提出受限玻爾茲曼機模型與深度信念網絡,成功地訓練多層神經網絡,解決了反向傳播算法局部最佳解問題,并把多層類神經網絡稱作“深度學習”,首次證明了大規模深度神經網絡學習的可能性。2007年,英偉達開發出統一計算架構(CUDA),研究人員透過CUDA可以輕松使用C語言開發GPU,使得GPU具有方便的編程環境可以直接編寫程序。2008年,英偉達推出Tegra芯片,作為最早的可用于人工智能領域的GPU,如今已成為英偉達最重要的AI芯片之一,主要用于智能駕駛領域。2009年,RajatRaina和吳恩達聯合發表利用GPU完成深度學習訓練的論文“Large-scaleDeepUnsupervisedLearningUsingGraphicProcessors”。2010年,IBM首次發布類腦芯片原型模擬大腦結構,該原型具有感知認知能力和大規模并行計算能力。

2012年,Krizhevsky與Hinton的團隊采用GPU架構結合卷積神經網絡(CNN)算法,在ImageNet大賽中,將圖像識別錯誤率降到18%,并在NIPS會議上發表圖像識別論文“ImageNetClassificationwithDeepConvolutionalNeuralNetworks”。這一突破性的成果,讓人們第一次驚喜地看到神經網絡的算力需求可被現行計算設備滿足。不過,這一成果也有它的美中不足:他們使用的GPU架構芯片并非針對神經網絡架構設計,其中包含許多運行神經網絡時不需要的架構設計,因此效率提升有限。就在同一年,GoogleBrain用1.6萬個GPU核的并行計算平臺訓練DNN模型,在語音和圖像識別等領域獲得巨大成功,2013年GPU開始廣泛應用于人工智能領域,高通公司發布Zeroth。2014年,中國科學研究院的陳天石博士(寒武紀創辦人)團隊發表以DianNao為名的人工智能專用加速芯片系列論文(包含DaDianNao、PuDianNao、ShiDianNao、Cambricon-X),開啟人工智能加速專用芯片(ASIC)的研究領域。也在同年,英偉達發布首個為深度學習設計的GPU架構Pascal,IBM發布第二代TrueNorth。

2015年,JasonCong在當年的國際FPGA大會上,發表1篇FPGA加速DNN算法的論文“OptimizingFPGA-basedAcceleratorDesignforDeepConvolutionalNeuralNetworks”,使得FPGAs迅速大火。很快地,2016年,Google發表TensorFlow框架設計的TPU芯片,而同年,采用TPU架構的AlphaGo出現,并擊敗人類世界冠軍棋士李世石。還是在同年,寒武紀研發出DIANNAO,FPGA芯片在云計算平臺得到廣泛應用。僅僅在2017年,谷歌TPU2.0發布,加強了訓練效能;英偉達發布Volta架構,推進GPU的效能大幅提升;華為麒麟970成為首個手機AI芯片;清華大學魏少軍教授團隊開發出Thinker原型,并隨后推出在算力和能效方面具有國際水平的系列Thinker人工智能芯片。

Lookonchain:一巨鯨將超9000枚ETH存入NFT市場Blur:金色財經報道,據鏈上分析師@Lookonchain披露數據顯示,一個“0x3Ac7”開頭的巨鯨地址已將9,025.5 ETH存入NFT市場Blur,價值約合1640萬美元,隨后該巨鯨開始在Blur平臺上購買和出售CryptoPunks以賺取獲得空投代幣機會的積分。[2023/4/2 13:40:05]

人工智能芯片的分類

2.1傳統CPU困局

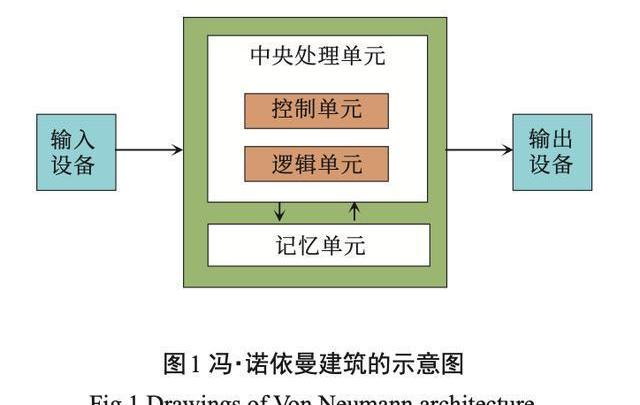

自20個世紀60年代早期開始,CPU(中央處理器)開始出現并使用在計算機工業中。現如今,雖然CPU在設計和實現上都發生了巨大變化,但是基于馮·諾依曼架構的CPU基本工作原理卻一直沒有發生很大變化。如圖1所示,馮·諾依曼架構分為中央處理單元(CPU)和存儲器,CPU主要由控制器和運算器兩大部件組成。在工作時,CPU每執行一條指令都需要從存儲器中讀取數據,根據指令對數據進行相應的操作,因此CPU不僅負責數據運算,而且需要執行存儲讀取、指令分析、分支跳轉等命令。同時可以通過提升單位時間內執行指令的條數,即主頻,來提升計算速度。但在人工智能深度學習領域中程序指令相對較少,但對大數據的計算需求很大,需要進行海量的數據處理。當用CPU執行AI算法時,CPU將花費大量的時間在數據/指令的讀取分析上,在一定的功耗前提下,不能夠通過無限制的加快CPU頻率和內存帶寬來達到指令執行速度無限制的提升。因此在這種情形下,傳統CPU結構缺點明顯,在人工智能芯片領域中的算力瓶頸問題很難解決。

2.2人工智能芯片中的后CPU時代

基于CPU的算力問題,近年來人工智能芯片領域的科學家們進行了富有成果的廣泛研究,主要集中在AI芯片目前的兩種發展方向。一個方向是繼續延續經典的馮·諾依曼計算架構,以加速計算能力為發展目標,主要分為并行加速計算的GPU(圖形處理單元)、半定制化的FPGA(現場可編程門陣列)、全定制化的ASIC(專用集成電路)。另一個方向就是顛覆傳統的馮·諾依曼計算架構,采用基于類腦神經結構的神經擬態芯片來解決算力問題。下面將對這兩個方向的人工智能芯片特點進行詳細描述。

2.2.1按架構分類

(1)圖形處理單元(graphicsprocessingunit,GPU)。GPU是相對較早的加速計算處理器,具有速度快、芯片編程靈活簡單等特點。由于傳統CPU的計算指令遵循串行執行方式,不能發揮出芯片的全部潛力,而GPU具有高并行結構,在處理圖形數據和復雜算法方面擁有比CPU更高的效率。在結構上,CPU主要由控制器和寄存器組成,而GPU則擁有更多的邏輯運算單元(arithmeticlogicunit,ALU)用于數據處理,這樣的結構更適合對密集型數據進行并行處理,程序在GPU系統上的運行速度相較于單核CPU往往提升幾十倍乃至上千倍。同時,GPU擁有了更加強大的浮點運算能力,可以緩解深度學習算法的訓練難題,釋放人工智能的潛能。但是GPU也有一定的局限性。深度學習算法分為訓練和推斷兩部分,GPU平臺在算法訓練上非常高效。但在推斷中對于單項輸入進行處理的時候,并行計算的優勢不能完全發揮出來。

(2)現場可編程門陣列(fieldprogrammablegatearray,FPGA)。FPGA是在PAL、GAL、CPLD等可編程器件基礎上進一步發展的產物。其基本原理是在FPGA芯片內集成大量的基本門電路以及存儲器,用戶可以通過更新FPGA配置文件(即燒入)來定義這些門電路以及存儲器之間的連線。這種燒入不是一次性的,因此,它既解決了定制電路靈活性的不足,又克服了原有可編程器件門電路數有限的缺點。與GPU不同,FPGA同時擁有進行數據并行和任務并行計算的能力,適用于以硬件流水線方式處理一條數據,且整數運算性能更高,因此常用于深度學習算法中的推斷階段。不過FPGA通過硬件的配置實現軟件算法,因此在實現復雜算法方面有一定的難度。

將FPGA和CPU對比可以發現兩個特點,一是FPGA沒有內存和控制所帶來的存儲和讀取部分,速度更快,二是FPGA沒有讀取指令操作,所以功耗更低。劣勢是價格比較高,編程復雜,整體運算能力不是很高。功耗方面,從體系結構而言,FPGA也具有天生的優勢。傳統的馮氏結構中,執行單元(如CPU核)執行任意指令,都需要有指令存儲器、譯碼器、各種指令的運算器及分支跳轉處理邏輯參與運行,而FPGA每個邏輯單元的功能在重編程(即燒入)時就已經確定,不需要指令,無需共享內存,從而可以極大地降低單位執行的功耗,提高整體的能耗比。FPGA最值得注意的例子可能是CNP,它進一步改進并重命名為NeuFlow,后來改編為nn-X。這些設計可以實現10~100KM/s操作(GOPS),功率僅為10W以下。

(3)專用集成電路(application-specificintegratedcircuit,ASIC)。目前以深度學習為代表的人工智能計算需求,主要采用GPU、FPGA等已有的適合并行計算的通用芯片來實現加速。在產業應用沒有大規模興起之時,使用這類GPU、FPGA已有的通用芯片可以避免專門研發定制芯片(ASIC)的高投入和高風險。但是,由于這類通用芯片設計初衷并非專門針對深度學習,因而天然存在性能、功耗等方面的局限性。隨著人工智能應用規模的擴大,這類問題日益突顯。

GPU作為圖像處理器,設計初衷是為了應對圖像處理中的大規模并行計算。因此,在應用于深度學習算法時無法充分發揮并行計算優勢。深度學習包含訓練和推斷兩個計算環節,GPU在深度學習算法訓練上非常高效,但對于單一輸入進行推斷的場合,并行度的優勢不能完全發揮。其次,GPU采用SIMT計算模式,硬件結構相對固定,無法靈活配置硬件結構。此外,運行深度學習算法能效低于FPGA。

雖然FPGA倍受看好,但其畢竟不是專門為了適用深度學習算法而研發,實際應用中為了實現可重構特性,FPGA內部有大量極細粒度的基本單元,但是每個單元的計算能力都遠低于CPU和GPU中的ALU模塊;其次,為實現可重構特性,FPGA內部大量資源被用于可配置的片上路由與連線,因此計算資源占比相對較低;再者,速度和功耗相對專用定制芯片(ASIC)仍然存在不小差距;而且FPGA價格較為昂貴,在規模放量的情況下單塊FPGA的成本要遠高于專用定制芯片。

因此,隨著人工智能算法和應用技術的日益發展,以及人工智能專用芯片ASIC產業環境的逐漸成熟,全定制化人工智能ASIC也逐步體現出自身的優勢。ASIC是專用定制芯片,定制的特性有助于提高ASIC的性能功耗比,缺點是電路設計需要定制,相對開發周期長,功能難以擴展。但在功耗、可靠性、集成度等方面都有優勢,尤其在要求高性能、低功耗的移動應用端體現明顯。比如谷歌的TPU、寒武紀的GPU,地平線的BPU都屬于ASIC芯片。

OpenAI CEO:ChatGPT不會取代搜尋引擎,但AI系統未來或許可以:2月8日消息,OpenAI 創始人兼首席執行官 Sam Altman 日前受訪時表示,ChatGPT 不會取代搜尋引擎,但相信 AI 系統將來或許能做到。Altman 指出,目前 ChatGPT 仍處于非常早期的階段。自己一開始做 ChatGPT 就相信它會成功,因此,雖然他對反響規模有些驚訝,但他確實此前就希望并預料到,ChatGPT 會受到人們的關注和喜愛。[2023/2/8 11:55:03]

(4)神經擬態芯片(類腦芯片)。在人工智能芯片中,傳統的馮·諾依曼架構存在著“馮·諾依曼瓶頸”,它降低了系統的整體效率和性能。為了從根本上克服這個問題,神經形態計算近年來已成為基于馮·諾依曼系統的這些傳統計算架構的最有吸引力的替代方案。術語“神經形態計算”首先由Mead在1990年提出,它是一種受大腦認知功能啟發的新計算范式。與傳統的CPU/GPU不同,生物腦(例如哺乳動物的大腦)能夠以高效率和低功耗在小區域中并行處理大量信息。因此,神經形態計算的最終目標是開發神經形態硬件加速器,模擬高效生物信息處理,以彌合網絡和真實大腦之間的效率差距,這被認為是下一代人工智能的主要驅動力。

神經擬態芯片不采用經典的馮·諾依曼架構,而是基于神經形態架構設計,是模擬生物神經網絡的計算機制,如果將神經元和突觸權重視為大腦的“處理器”和“記憶”,它們會分布在整個神經皮層。神經擬態計算從結構層面去逼近大腦,其研究工作可分為兩個層次,一是神經網絡層面,與之相應的是神經擬態架構和處理器,以IBMTruenorth為代表,這種芯片把定制化的數字處理內核當作神經元,把內存作為突觸。

其邏輯結構與傳統馮·諾依曼結構不同:內存、CPU和通信部件完全集成在一起,因此信息的處理在本地進行,克服了傳統計算機內存與CPU之間的速度瓶頸問題。同時神經元之間可以方便快捷地相互溝通,只要接收到其他神經元發過來的脈沖(動作電位),這些神經元就會同時做動作;二是神經元與神經突觸層面,與之相應的是元器件層面的創新。如IBM蘇黎世研究中心宣布制造出世界上首個人造納米尺度的隨機相變神經元,可實現高速無監督學習。

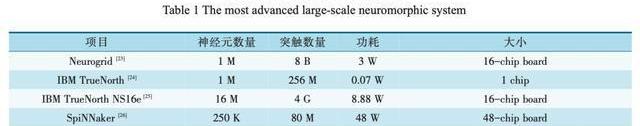

當前,最先進的神經擬態芯片仍然遠離人類大腦的規模(1010個神經元,每個神經元有103~104個突觸),至多達到104倍,如表1所示。為了達到在人腦中規模,應將多個神經擬態芯片集成在電路板或背板上,以構成超大規模計算系統。神經擬態芯片的設計目的不再僅僅局限于加速深度學習算法,而是在芯片基本結構甚至器件層面上改變設計,希望能夠開發出新的類腦計算機體系結構,比如采用憶阻器和ReRAM等新器件來提高存儲密度。這類芯片技術尚未完全成熟,離大規模應用還有很長的距離,但是長期來看類腦芯片有可能會帶來計算機體系結構的革命。

2.2.2按功能分類

根據機器學習算法步驟,可分為訓練(training)和推斷(inference)兩個環節。訓練環節通常需要通過大量的數據輸入,訓練出一個復雜的深度神經網絡模型。訓練過程由于涉及海量的訓練數據和復雜的深度神經網絡結構,運算量巨大,需要龐大的計算規模,對于處理器的計算能力、精度、可擴展性等性能要求很高。目前市場上通常使用英偉達的GPU集群來完成,Google的TPU2.0/3.0也支持訓練環節的深度網絡加速。

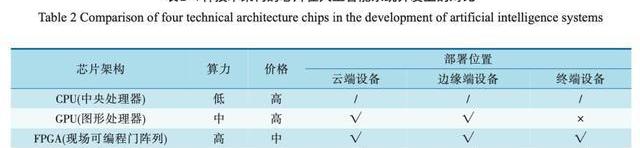

推斷環節是指利用訓練好的模型,使用新的數據去“推斷”出各種結論。這個環節的計算量相對訓練環節少很多,但仍然會涉及到大量的矩陣運算。在推斷環節中,除了使用CPU或GPU進行運算外,FPGA以及ASIC均能發揮重大作用。表2是4種技術架構的芯片在人工智能系統開發上的對比。

2.2.3按應用場景分類

主要分為用于服務器端(云端)和用于移動端(終端)兩大類。

服務器端:在深度學習的訓練階段,由于數據量及運算量巨大,單一處理器幾乎不可能獨立完成1個模型的訓練過程,因此,負責AI算法的芯片采用的是高性能計算的技術路線,一方面要支持盡可能多的網絡結構以保證算法的正確率和泛化能力;另一方面必須支持浮點數運算;而且為了能夠提升性能必須支持陣列式結構(即可以把多塊芯片組成一個計算陣列以加速運算)。在推斷階段,由于訓練出來的深度神經網絡模型仍非常復雜,推斷過程仍然屬于計算密集型和存儲密集型,可以選擇部署在服務器端。

移動端(手機、智能家居、無人車等):移動端AI芯片在設計思路上與服務器端AI芯片有著本質的區別。首先,必須保證很高的計算能效;其次,在高級輔助駕駛ADAS等設備對實時性要求很高的場合,推斷過程必須在設備本身完成,因此要求移動端設備具備足夠的推斷能力。而某些場合還會有低功耗、低延遲、低成本的要求,從而導致移動端的AI芯片多種多樣。

人工智能芯片研究現狀

3.1研究背景

人工智能芯片的核心為神經網絡算法的實現。深度神經網絡(DNN)已經在自然語言處理、機器視覺、語音識別、醫學影像分析等眾多人工智能領域取得了重大突破。深度學習主要分為傳統卷積神經網絡(CNN)和遞歸神經網絡(RNN),其依賴于大數據集的反復訓練和大量浮點運算推理運算,這對計算機算力要求較高,訓練時間長,功耗極大。以AlphaGo為例,其基于1920個中央處理單元和280個圖形處理單元,功耗為1MW,這幾乎是人腦能耗(~20W)的5萬倍。近年來,人工智能被視為有極大的潛力應用于物聯網和邊緣計算領域中,因此需要具備高能效、快速預測,在線學習的能力,以避免向后端或服務器發送大量的數據。

人工智能算法、架構、電路、器件等各個層面得到了很大的改進和優化,以減少推理的能量消耗,同時保持分類精度等性能指標。通過定制ASIC設計實現節能推理硬件加速器的工作已經實現了相當高的能效(1TFlops/W),但基于反向傳播的深度學習算法需要頻繁地從遠程傳播誤差信號,因此很難實現有效的在線學習。由于能量效率低下和缺乏有效的在線學習方法,以CNN和RNN為代表的許多深度學習算法不適合以事件驅動和對能效要求極高的新興人工智能應用,例如物聯網智能傳感器和邊緣計算等。

在此背景下,人工智能領域科學家提出脈沖神經網絡(SNN),其被譽為第三代人工神經網絡。

SNN在神經元模型之間使用時序脈沖序列來表示、傳輸和處理信息,來保證了更快的在線學習和更高的能量效率。相比傳統的人工神經網絡(CNN和RNN),SNN具備了更多獨特的仿腦特性,包括信息的脈沖表示、事件驅動的信息處理和基于脈沖的局部學習規則等,更加接近于生物神經網絡中的學習和記憶機制。因此,由于脈沖神經網絡其快速的在線學習、極高的能量效率、與人腦的高度相似性,近年來是人工智能科學領域極具科學意義的研究課題。

Polychain、DCG、1kx、Multicoin 等聯合推出去中心化資產管理市場 AladdinDAO:6月2日消息,數十家加密貨幣投資機構聯合推出去中心化資產管理市場AladdinDAO,旨在通過加密經濟學的機制設計和去中心化自治組織(DAO)的方式改變風險投資的現有模式,激勵DeFi參與者為社區成員選擇最佳流動性挖礦項目,解決DeFi投資領域信息不對稱的問題。

據悉,AladdinDAO的創始成員包括Polychain、DCG、1kx、Multicoin Capital、CMS、Nascent、Alameda、DeFiAlliance、Robert Leshner、Kain Warwick、Hart Lambur、AlexPack、Ashwin Ramachandran和Sharlyn Wu。

據AladdinDAO介紹,該組織將是一個提供一站式流動性挖礦體驗的平臺,并使用博弈論來構建去中心化的資產管理市場,將以簡單的策略入手,使投資者可以直接參與所選定的DeFi流動性挖礦項目,最終將擴展到由社區開發者和DAO成員提供的多策略產品。[2021/6/2 23:05:49]

3.2研究現狀

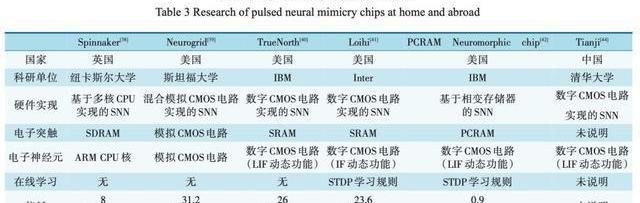

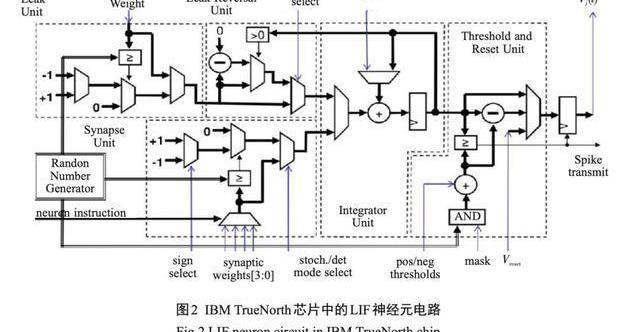

近年來,世界上著名的學術研究機構和國際半導體公司都在積極研究和開發基于脈沖的神經擬態電路。如表3所示,基于SNN的神經擬態計算硬件比基于傳統DNN的硬件加速器具有更高的能量效率。大多數最先進的神經擬態計算芯片都是基于成熟的CMOS硅技術對SNN進行ASIC設計,通過SRAM等存儲器模擬實現人工突觸,并利用關鍵的數字或模擬電路仿生實現人工神經元。其中最具有代表性的是IBM公司研發的基于CMOS多核架構TrueNorth芯片,當模擬100萬個神經元和2億5000萬個突觸時,該芯片僅消耗70mW的功耗,每個突觸事件僅消耗26pJ的極高能量效率。然而,為了模仿生物突觸和神經元的類腦特性,電子突觸和神經元需要高度復雜的CMOS電路來實現所需的人工突觸和神經元的功能,如圖2所示。

以IBM的TrueNorth芯片為例,它包含54億個晶體管,在28nm工藝下占據4.3cm2的面積。因此,這一類基于脈沖的神經擬態CMOS硬件電路使用大量的晶體管,并導致耗費非常大的芯片面積。加之,現有的大多數神經擬態芯片由于其計算單元與存儲單元在局部依然是分離的,這在用于神經元的CMOS邏輯電路和用于突觸的SRAM電路之間依然存在局部的存儲壁壘問題和能量效率問題,所以實際上還不是真正意義上的非馮·諾依曼體系結構。不過最新的具有三維堆疊能力的非易失性存儲器(NVM)技術或存內計算技術(in-memorycomputing)有望解決這一問題。

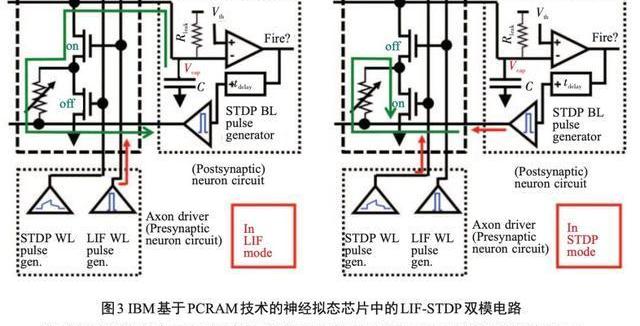

另一項由IBM開發的基于新型NVM技術的脈沖神經網絡功能芯片證明了在非馮·諾依曼體系結構中使用相變存儲器(PCRAM)這一創新的NVM技術能夠實現極低的能耗(僅為0.9pJ/bit)。由占據在交叉點的相變存儲電阻組成了十字交叉整列結構,連同CMOS模擬電路一起實現脈沖時序依賴可塑性(STDP)學習規則的突觸可塑性功能和帶泄漏積分放電(LIF)的神經元功能,如圖3所示。但是,由于預測精度的問題,該芯片只能執行簡單的應用任務,完成基本模式的聯想學習。IBM的基于脈沖的神經擬態芯片反映了在人工神經元和突觸,以及新興的NMV技術的研究領域里最新的科研進展。

在借鑒國外研究工作的同時,我國也大力發展基于脈沖的神經擬態芯片研究。清華大學團隊提出一款基于CMOS技術的多核架構類腦芯片天機一號,實現了支持LIF的人工神經元功能。北京大學團隊提出了一種基于憶阻器陣列的神經擬態芯片,實現了簡化的LIF功能和簡單的赫伯學習機制。憶阻器是一種新型的NVM器件,具有獨特的模擬特性和可擴展性,并且由于其出色的能耗效率和器件特性,可以進一步提高神經擬態芯片的集成規模和整體效能。

至今基于脈沖的神經擬態芯片的主要研究方法是通過對生物神經科學中已發現的生物行為特征進行直接模擬和仿生實現,包括算法建模、電路創新、新型器件技術等各個層面的研究和探索。雖然基于神經擬態計算算法的人工智能芯片技術近年來已得到很大的發展和進步,但是依然難以實現所有的已知生物學習機制,僅通過對SNN模型的優化來達到近似或模仿一些生物現象從而實現一些簡單的學習功能,比如路徑規劃和手寫識別。這些簡化的類腦模型包括基于脈沖時序依賴的更新規則的突觸模型和基于確定的線性積分放電動態的神經元模型。

人工智能芯片產業現狀

4.1產業現狀評述

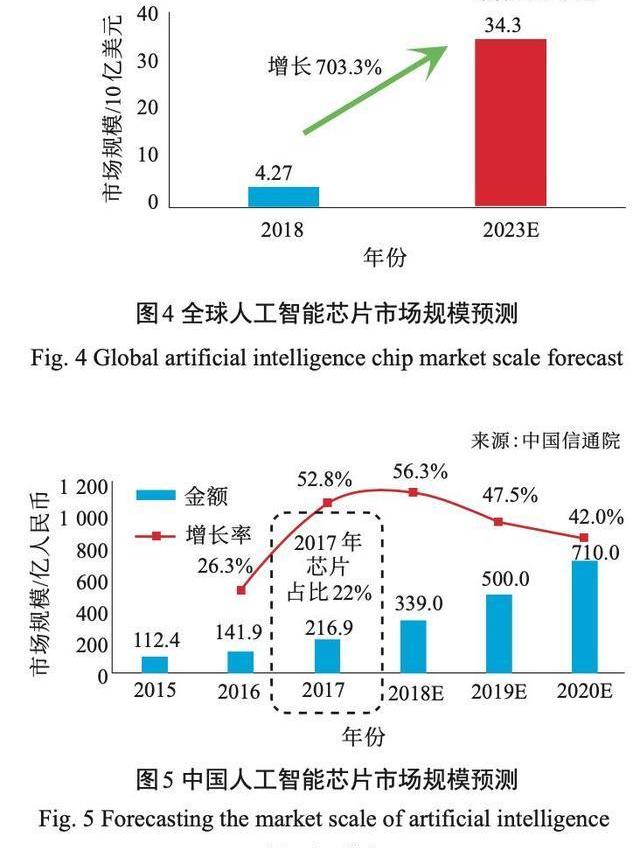

AI芯片是芯片產業和人工智能產業整合的關鍵,特別是AI系統芯片。根據Gartner的預測數據,未來5年內全球人工智能芯片市場規模將呈飆升趨勢,自2018年的42.7億美元,升高至343億美元,增長已超過7倍,可見AI芯片市場有較大增長空間,如圖4所示。

對于中國AI芯片市場,根據中國信通院的數據報告,中國的人工智能市場規模預計在2018年超過300億人民幣,而2019年后將超過500億人民幣。市場年度增長率,將從2017年的52.8%上升至2018年的56.3%,隨后逐年下降,在2020年降至42.0%。其中,2017年芯片銷售額占人工智能市場規模的22%,約47.7億人民幣,如圖5所示。

現今,中國已有超過20家以上的新創AI芯片設計企業,融資總額超過30億美元。AI芯片行業生命周期正處于幼稚期,市場增長快,至2022年將從2018年的42.7億美元,發展至343億美元,但芯片企業與客戶的合作模式仍在探索中。為了生存,行業逐漸出現上下游整合的趨勢。云端(含邊緣端)服務器、智慧型手機和物聯網終端設備等3個場景,是目前AI芯片企業的主要落地市場,少數企業則是面向未來的自動駕駛汽車市場。這些市場都具有千萬量級出貨量或百億美元銷售額等特征。

然而,中國長期面臨集成電路的進口額大于出口額的情況,根據海關總署的統計,如圖6所示,2018年進口總額正式突破3000億美元,約達3121億美元,同比2017年增長了19.8%。相較之下,集成電路的出口總額在2018年時僅846億美元,尚不到進口額的1/3,而同年原油進口額約為2400億美元,由此可見,中國極度依賴于國外芯片制造商。目前國內芯片制造技術尚待提高,但由于半導體的分工模式相當成熟,國內芯片設計企業并不需要擔心芯片生產問題。

加密風投基金PolychainCapital已出售所持全部MKR代幣1,315枚:加密風投基金PolychainCapital已于兩日前出售所持MKR代幣1,315.93枚。截至目前,該地址共有48,089枚ETH以及570枚yearn.finance代幣YFI。[2020/12/6 14:16:52]

4.2AI芯片產業鏈

AI芯片產業鏈主要分成設計—制造/封測—系統。

上游:主要是芯片設計,按商業模式,可再細分成3種:IP設計、芯片設計代工和芯片設計。IP設計即設計芯片用的IP核(IPcore)。

(2)中游:包含兩大類,分別是晶圓制造和封裝測試,晶圓不僅是在封裝時測試,制造后也會有一次測試,封裝后再有一次。

(3)下游:分成銷售和系統集成(systemintegration)企業,其中提供軟硬件集成解決方案的企業會被歸屬在系統集成商中,例如人工智能解決方案商。

4.3AI芯片商業模式

按半導體上游與中游的集成與否,市場分成兩種商業模式。

(1)垂直集成模式:又稱IDM,歸屬于該模式的企業業務同時包含設計和制造/封測。IDM模式的代表企業是英特爾和三星。

(2)垂直分工模式:采取分工模式的企業僅只專營一項業務,比如英偉達和華為海思僅有芯片設計,沒有制造業務,稱作Fabless;而臺積電和中芯國際僅代工制造,不涉及芯片設計,稱作Foundry。

4.4AI芯片設計產業模式

芯片設計的產業模式分為IP設計、芯片設計代工和芯片設計3種。

(1)IP設計:IP設計相較于芯片設計是在產業鏈的更頂層,以IP核授權收費為主。傳統的IP核授權企業以安謀(Arm)為代表,新創的AI芯片企業雖然也可設計出新型IP核,但因授權模式不易以規模效應創造出可觀的收入,新創企業一般不以此作為主要盈利模式。另外還有提供自動化設計(EDAtool)和芯片設計驗證工具的Cadence和Synopsys,也在積極部署人工智能專用芯片領域。

(2)芯片設計代工:芯片設計代工和制造業的代工一樣,提供設計代工服務的企業,并不能在產品上貼上自己的標簽,也不能對外宣稱該產品由自己設計。芯原科技已經從事相關服務多年,也和恩智浦(NXP)有合作關系。

(3)芯片設計:大部分的人工智能新創企業是以芯片設計為主,但在這個領域中存在傳統強敵,如英偉達、英特爾、賽靈思(Xilinx)和恩智浦,因而目前只有少數新創AI芯片設計企業會進入傳統芯片企業的產品領域,例如,寒武紀與英偉達競爭服務器芯片市場,地平線與英偉達及恩智浦競爭自動駕駛芯片市場,其余企業則是在物聯網場景上布局,像是提供語音辨識芯片的云知聲,提供人臉辨識芯片的中星微,以及提供邊緣計算芯片的耐能科技。

半導體的垂直分工模式雖有助于純芯片設計企業的生存,不過單一芯片難以單獨實現復雜功能,于是有些企業開始提供芯片集成服務,集成后的產品稱作系統或IC(integratedcircuit)模塊,在人工智能領域則稱為AI系統或AI模塊。一般而言,人工智能企業會同時提供算法和芯片的集成服務,該類企業通常被稱為“人工智能方案解決商”,或稱AI一站式服務(AITurnkey)。

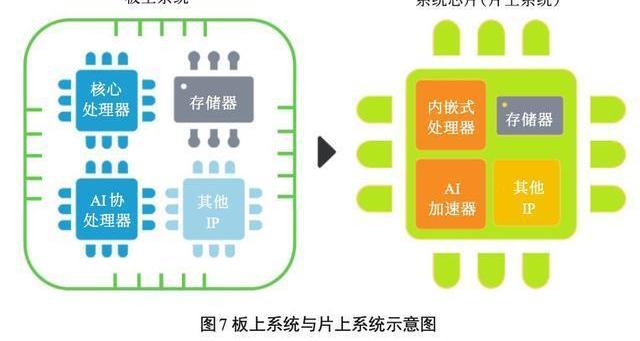

4.5AI芯片產品類型

根據集成的產品類型可再分成兩類,即硬件集成和軟件集成。(1)硬件集成:將不同功能的芯片集成于同一塊電路板(PCB)上,即被稱為硬件集成,其中會包含核心處理器、協處理器(加速芯片)、存儲器和其他零件。硬件集成初級的產品是板上系統(systemonboard),但終極目標是將多個芯片集成在一塊芯片上形成系統芯片,或稱片上系統(systemonchip),如圖7所示。

(2)軟件集成:根據集成硬件的需求或純粹軟件集成的需求,軟體工程師將不同軟件(software)和固件(firmware)集成起來安裝到板上系統或片上系統中。因AI芯片設計的難度并沒有過往的CPU高,為增加行業競爭優勢,人工智能企業除本身提供的系統集成服務外,也開始往芯片設計方向整合。與此同時,AI芯片企業為了加速產品落地,減少尋找客戶的難度,會同時兼任芯片企業和集成商這兩種身份。于是,目前行業呈現人工智能與芯片產業雙向整合的情況。整合后的AI系統集成商可以將更高性能、更低價格、更低功耗的系統芯片(片上系統)方案提供給客戶。

4.6存在的問題

因系統芯片開發技術復雜,人才缺口成為首要難題。系統芯片設計的關鍵技術包含但不限于以下6項:(1)總線架構技術;(2)IP核可復用技術;(3)軟硬件協同設計技術;(4)時序分析技術;(5)驗證技術;(6)可測性設計技術。以上關鍵技術皆涉及跨學科知識,且開發流程復雜,工序可多達40個,每個工序都需要一位專業工程師負責執行工作,開發過程需要前后反復多次驗證設計,避免流片失敗。

系統芯片(SoC)設計與AI加速芯片(ASIC)設計相比,前者的設計難度更高,兩者之間的差異主要表現在以下兩點:第一,系統芯片設計需要更加了解整個系統的運作,由此可更合理的定義芯片架構,使得軟硬件集成達到系統最佳工作狀態。第二,系統芯片設計是以IP核復用為基礎,基于IP模塊的大規模集成電路設計是系統芯片實現的關鍵。綜上所述,系統芯片設計團隊或以系統芯片為目標創立的AI芯片企業,首先面臨的是人才技術儲備問題,再來才是后續問題。

4.7AI芯片落地情況分析

現如今,云端與終端皆有AI芯片落地。其中服務器、手機、智能家居、自動駕駛是主要落地場景。由于AI芯片是實現人工智能用途或深度學習應用的專用芯片,芯片與算法的結合程度高,因此接下來將會按照用途、部署位置以及應用場景來討論AI芯片的落地及相關市場規模。

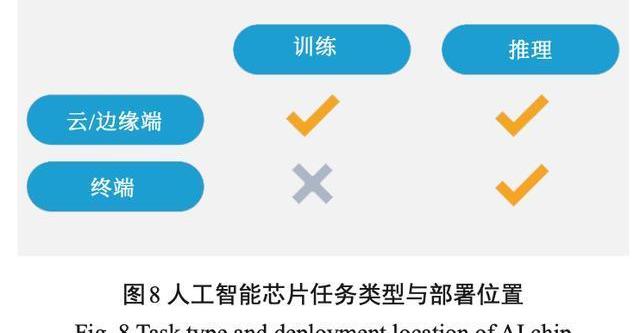

在人工智能的技術基礎上,深度學習算法對于使用者來說會有“訓練”和“推理”兩種用途,這是因為深度學習算法就如同人類的大腦一樣,需要經過學習才能做出判斷,就像人要能辨識貓狗,首先需要學習了解貓狗的特征。因此,企業在部署人工智能設備時,也會經歷算法/模型訓練,再進行推理應用。一般來說,如圖8所示,執行訓練任務的AI芯片僅會部署在云端和邊緣端上,而執行推理任務的AI芯片會部署在云端、邊緣端和終端上,應用范圍更廣,這是因為推理的算力需求較低。應用場景和深度學習算法的類型有關。

計算機視覺通常會使用卷積神經網絡(CNN)訓練模型,自然語言處理(NLP)則會使用循環神經網絡(RNN)訓練模型,AI芯片也主要應用于視覺和語言。但是,相較于CNN和RNN等較舊的算法,現在深度學習算法持續在演變中,因此行業應用時并不局限于上述兩類算法。每家人工智能企業都有自己獨特的算法,AI芯片企業也是一樣,會根據自己的改良算法來設計AI芯片。

動態 | 基于EOS的電子郵件dmail和Eclipse展開合作:據引力觀察消息,基于EOS的電子郵件和Eclipse展開合作。Eclipse是自動化的資源管理服務,能夠為DApp的用戶自動提供CPU和NET資源。[2019/4/16]

4.7.1云端市場

隨著云端市場需求不斷上升,服務器AI芯片的市場前景樂觀。按照AI芯片的部署位置,可簡單將AI芯片市場分成云端(邊緣端并入云端)市場和終端市場兩類,具有云計算需求的行業主要是金融業、醫療服務業、制造業、零售/批發以及政府部門等5大行業。

根據IDC數據,如圖9所示,云計算需求增長快速,在2018~2019年全球云計算支出將迎來大幅度增長,5大行業的支出最低增長17.3%,最高26.3%,其中以醫療業的需求最高,超100億美元。與此同時,根據IDC數據,2018年第三季度全球服務器設備的出貨量達320萬臺,營收達234億美元以上,從出貨增長率來看,2018年全年營收達1000億美元以上,遠超過2017年營收669億美元。

云計算支出的快速增長,代表云計算的需求旺盛。服務器的出貨量持續提升,也意味著部署服務器的AI芯片的需求量跟著提升。由此可見,云端芯片的市場未來將快速增長。

4.7.2終端市場

當前的終端市場上,主要有兩大落地場景,一個是智慧型手機,另一個是物聯網設備。手機又被稱作移動端,在智慧型手機上,AI芯片的主要任務是拍照后的圖像處理,以及協助智慧助理的語音處理。根據IDC的數據,全球智慧型手機出貨量已經連續兩年超過14億部,其中全球前5大廠商中有3家是中國企業,按2018年出貨量由高到低排序依次為,華為2.06億部、小米1.23億部,和OPPO1.13億部。

除手機之外,物聯網也是當前終端市場中重要的一部分。根據IDC數據,物聯網的市場主要在產業應用上,制造業、運輸業和公用事業合計超過3290億美元,其中消費性產品(包含智能家居、穿戴設備、智慧座艙等)占1080億美元。AI芯片在物聯網產品上的應用主要有兩個用途,一個是視覺AI芯片,另一個是語音AI芯片,但因為自然語言處理的AI產品開發難度高,目前新創AI芯片企業主要切入的市場是計算機視覺設備的落地場景,比如家庭安全設備。根據IDC數據,全球智能家居市場中的家庭安全設備出貨量已達9770萬臺,而智能音箱也有9980萬臺設備,兩類設備至2022年都會增長超過2億以上。總而言之,物聯網在智能家居場景落地可以保證具有千萬銷售量的市場。

未來,自動駕駛將是終端芯片應用的另一塊重要場景。根據MARKLINES的數據,2014年中國汽車銷售量為2349.2萬輛,2018年已增長至2808.1萬輛。中國千萬量級汽車銷售市場對于開發自動駕駛技術的企業具有極大吸引力。縱然中國汽車銷售量已達千萬量級,但目前電動車銷售量仍不及整體汽車銷售量的10%,而自動駕駛技術的發展是以電動車為主,電動車市場有很大的增長空間。

結論

目前,我國的人工智能芯片行業發展尚處于起步階段。長期以來,中國在CPU、GPU、DSP處理器設計上一直處于追趕地位,絕大部分芯片設計企業依靠國外的IP核設計芯片,在自主創新上受到了極大的限制。然而,人工智能的興起,無疑為中國在處理器領域實現彎道超車提供了絕佳的機遇。人工智能領域的應用目前還處于面向行業應用階段,生態上尚未形成壟斷,國產處理器廠商與國外競爭對手在人工智能這一全新賽場上處在同一起跑線上。因此,基于新興技術和應用市場,中國在建立人工智能生態圈方面將大有可為。

由于我國特殊的環境和市場,國內AI芯片的發展目前呈現出百花齊放、百家爭鳴的態勢,AI芯片的應用領域也遍布股票交易、金融、商品推薦、安防、早教機器人以及無人駕駛等眾多領域,催生了大量的人工智能芯片創業公司,如北京地平線信息技術有限公司、北京深鑒科技有限公司、北京中科寒武紀科技有限公司等。盡管如此,國內公司卻并未如國外大公司一樣形成市場規模,反而出現各自為政的散裂發展現狀。除了新興創業公司,國內研究機構如北京大學、清華大學、中國科學院等在AI芯片領域都有深入研究;而其他公司如百度和北京比特大陸科技有限公司等亦在積極布局人工智能芯片產業。可以預見,未來誰先在人工智能領域掌握了生態系統,誰就掌握住了這個產業的主動權。

參考文獻YANNLC,CORTESC.TheMNISTdatabaseofhand-writtendigits..http://yann.lecun.com/exdb/mnist/.TAIGMANY,YANGM,RANZATOMA,etal.Deep-face:Closingthegaptohumanlevelperformanceinfaceverification//IEEEConferenceonComputerVisionandPatternRecognition.IEEE,2014:1701-1708.AmazonAlexa.WaystobuildwithAlexa...https://developer.amazon.com/alexa.AppleSiri.Siridoesmorethanever,evenbeforeyouask..http://www.apple.com/ios/siri/.MicrosoftCortanaPersonalAssistant.Cortana.Yourintelligentassistantacrossyourlife..https://www.microsoft.com/en-us/cortana.QUIGLEYM,CONLEYK,GERKEYB,etal.ROS:anopen-sourceRobotOperatingSystem//ICRAworkshoponopensourcesoftware.2009:5.URMSONC,BAGNELLJA,BAKERCR,etal.Tartanracing:amulti-modalapproachtotheDARPAurbanchallenge.Technicalreport,CarnegieMellonUniversity,2007.SILVERD,HUANGA,MADDISONCJ,etal.Masteringthegameofgowithdeepneuralnetworksandtreesearch.Nature,2016,529(7587):484-489.EMILIOM,MOISESM,GUSTAVOR,etal.Pac-mAnt:optimizationbasedonantcoloniesappliedtodevelopinganagentforMs.Pac-Man//IEEESymposiumonComputationalIntelligenceandGames(CIG).IEEE,2010:458-464.CHENT,DUZ,SUNN,etal.DianNao:asmallfootprinthighthroughputacceleratorforubiquitousmachine-learning//128InternationalConferenceonArchitecturalSupportforProgrammingLanguagesandOperatingSystems(ASPLOS).2014:269-284.CHENY,LUOT,LIUS,etal.DaDianNao:amachine-learningsupercomputer//201447thAnnualIEEE/ACMInternationalSymposiumonMicroarchitecture(MICRO).IEEE,2014:609-622.LIUD,CHENT,LIUS,etal.PuDianNao:apolyvalentmachinelearningaccelerator//InternationalConferenceonArchitecturalSupportforProgrammingLanguagesandOperatingSystems(ASPLOS).2015:369-381.DUZ,FASTHUBERR,CHENT,etal.ShiDianNao:Shiftingvisionprocessingclosertothesensor//InternationalSymposiumonComputerArchitecture(ISCA).2015:92-104.JOUPPINP,YOUNGC,PATILN,etal.In-datacenterperformanceanalysisofatensorprocessingunit//InternationalSymposiumonComputerArchitecture(IS-CA).2017:1-12.KAPOOHT.VonNeumannarchitecturescheme.TheInnovationinComputingCompanion,257-259.https://en.wikipedia.org/wiki/Von_Neumann_architecture.FARABETC,POULETC,HANJY,etal.CNP:anfpga-basedprocessorforconvolutionalnetworks//InternationalConferenceonFieldProgrammableLogicandApplications(FPL).2009:32-37.FARABETC,MARTINIB,CORDAB,etal.NeuFlow:aruntimereconfigurabledataflowprocessorforvision//IEEEComputerSocietyConferenceonComputerVisionandPatternRecognitionWorkshops(CVPRW).IEEE,2011:109-116.GOKHALEV,JINJ,DUNDARA,etal.A240G-ops/smobilecoprocessorfordeepneuralnetworks//IEEEConferenceonComputerVisionandPatternRecognitionWorkshops(CVPRW).IEEE,2014:682-687.NEUMANNJV.Theprinciplesoflarge-scalecomputingmachines.AnnalsoftheHistoryofComputing,1981,3(3):263-273.MEADC.Neuromorphicelectronicsystems.ProceedingsoftheIEEE,1990,78(10):1629-1636.STRUKOVDB.Nanotechnology:smartconnections.Nature,2011,476(7361):403-405.JEFFH,BLAKESLEES.Onintelligence.London:Macmillan,2007.BENJAMIN,VARKEYB,GAOP,etal.Neurogrid:amixed-analogdigitalmultichipsystemforlarge-scaleneuralsimulations.ProceedingsoftheIEEE,2014,102(5):699-716.MEROLLAPA,ARTHURJV,ALVAREZ-ICAZAR,etal.Amillionspiking-neuronintegratedcircuitwithascalablecommunicationnetworkandinterface.Science,2014,345(6197):668-673.CASSIDYAS,ALVAREZ-ICAZAR,AKOPYANF.Real-timescalablecorticalcomputingat46giga-synapticOPS/wattwith~100×speedupintime-to-solutionand~100,000×reductioninenergy-to-solution//SC'14:ProceedingsoftheInternationalConferenceforHighPerformanceComputing,Networking,StorageandAnalysis.IEEE,2014.FURBERSB,GALLUPPIF,TEMPLES,etal.Thespinnakerprojec.ProceedingsoftheIEEE,2014,102(5):652-665.SCHEMMELJ,BRIIDERLED,GRIIBLA,etal.Awaferscaleneuromorphichardwaresystemforlarge-scaleneuralmodeling//Proceedingsof2010IEEEInternationalSymposiumonCircuitsandSystems.IEEE,2010.LECUNY,BENGIOY,HINTONG,etal.Deeplearning.Nature,2015,521(7553):436-444.KELLERJ,PEREZO.ImprovingMCTSandneuralnetworkcommunicationincomputergo.WorcesterPolytechnicInstitute,2016.ZHANGSJ,DUZD,ZHANGL,etal.Cambricon-Xanacceleratorforsparseneuralnetworks.201649thAnnualIEEE/ACMInternationalSymposiumonMicroarchitecture(MICRO).IEEE,2016.KOWALIKJS.Parallelcomputationandcomputersforartificialintelligence.SpringerScience&BusinessMedia,2012.VERHELST,M,MOONSB.EmbeddeddeepneuralnetworkprocessingalgorithmicandprocessortechniquesbringdeeplearningtoIoTandedgedevices.IEEESolid-StateCircuitsMagazine,2017,9(4):55-65.JOUPPINP,YOUNGC,PATILN,etal.In-datacenterperformanceanalysisofatensorprocessingunit.44thInternationalSymposiumonComputerArchitecture(ISCA),2017.SZEV,CHENYH,YANGTJ,etal.Efficientprocessingofdeepneuralnetworksatutorialandsurvey.ProceedingsoftheIEEE,2017,105(12).BENNISM.Smartphoneswillgetevensmarterwithondevicemachinelearning.IEEESpectrum,2018.https://spectrum.ieee.org/tech-talk/telecom/wireless/smart-phones-will-get-even-smarter-with-ondevice-machine-learning.MAASSW.Networksofspikingneurons:thethirdgenerationofneuralnetworkmodels.NeuralNetworks,1997,10(9):1659-1671.MEADC.Neuromorphicelectronicssystem.ProceedingsoftheIEEE,1990,78(10):1629-1636.PAINKRASE,PLANALA,GARSIDEJ,etal.SpiNNaker:a1-W18-coresystem-on-chipformassively-parallelneuralnetworksimulation.IEEEJournalofSolidStateCircuitsPage(s),2013,48(8):1943-1953.BENJAMINBV,GAOP,MCQUINNE,etal.Neu-rogridamixed-analogdigitalmultichipsystemorlarge-scaleneuralsimulations.ProceedingsofIEEE,2014,102(5):699-716.MEROLLAPA,ARTHURJV,ALVAREZ-ICAZAR,etal.Amillionspiking-neuronintegratedcircuitwithascalablecommunicationnetworkandinterface.Science,2014,345(6197):668-673.DAVIESM,SRINIVASAN,LINTH,etal.Loihianeuromorphicmanycoreprocessorwithon-chiplearning.IEEEMicro,2018,38(1):82-99.KIMS.NVMneuromorphiccorewith64k-cell(256-by-256)phasechangememorysynapticarraywithon-chipneuroncircuitsforcontinuousin-situlearning//IEEEInternationalElectronDevicesMeeting(IEDM).IEEE,2015.CHUM,KIMB,PARKS,etal.NeuromorphichardwaresystemforvisualpatternrecognitionwithmemristorarrayandCMOSneuron.IEEETransactionsonIndustrialElectronics,2015,62(4):2410-2419.SHILP,PEIJ,DENGN,etal.Developmentofaneuromorphiccomputingsystem//IEEEInternationalElectronDevicesMeeting(IEDM).IEEE,2015.JIANGYN,HUANGP,ZHU,DB,etal.DesignandhardwareimplementationofneuromorphicsystemswithRRAMsynapses.IEEETransactionsonCircuitsandSystemsI:RegularPapers,2018,65(9):2726-2738.YUSM,CHENPY.Emergingmemorytechnologies:recenttrendsandprospects.ProceedingsoftheIEEE,2016,8(2):43-56.SURIM.CBRAMdevicesasbinarysynapsesforlow-powerstochasticneuromorphicsystems:auditoryandvisualcognitiveprocessingapplications//ProceedingofIEEEInternationalElectronDevicesMeeting(IEDM),2012:3-10.WANGZ.Memristorswithdiffusivedynamicsassynapticemulatorsforneuromorphiccomputing.NatureMaterials,2017,16(1):101-108.YANGJJ,STRUKOVDB,STEWARTDR.Memristivedevicesforcomputing.NatureNanotechnology,2013,8(1):13-24.JOSH.Nanoscalememristordeviceassynapseinneuro-morphicsystems.Nanoletters,2010,10(4):1297-1301.OHNOT.Short-termplasticityandlong-termpotentiationmimickedinsingleinorganicsynapses.NatureMaterials,2011,10(8):591-595.WANG,ZR,JOSHIS,SAVEL’EVSE,etal.Memristorswithdiffusivedynamicsassynapticemulatorsforneuromorphiccomputing.NatureMaterials,2017,16(1):101-108.來源:任源,潘俊,劉京京,等.人工智能芯片的研究進展.微納電子與智能制造,2019,1(2):20-34.

RENYuan,PANJun,LIUJingjing,etal.Overviewofartificialintelligencechipdevelopment.Micro/nanoElectronicsandIntelligentManufacturing,2019,1(2):20-34.

《微納電子與智能制造》刊號:CN10-1594/TN

主管單位:北京電子控股有限責任公司

主辦單位:北京市電子科技科技情報研究所、北京方略信息科技有限公司

福利直達!CSDN技術公開課評選進行中一文告訴你,如何使用Python構建一個“谷歌搜索”系統|內附代碼利用丁香園數據生成疫情分布地圖|博文精選小米10年再創業,高端5G手機和AIoT有多少機會?在家辦公,我比上班還累你信嗎?2019年度區塊鏈安全復盤總結

Tags:人工智能EEEFPG人工智能技術應用學人工智能后悔死了人工智能考研考哪些科目EEE幣是什么幣FPG幣FPG價格

在現今的家庭生活中,做家務的重任已經不單單由女性扛起了,解放雙手也好像成了全民的需求,所以越來越多的掃地機器人、吸塵器等家電進入普通家庭生活中,本次有幸體驗到追覓V10無線吸塵器.

1900/1/1 0:00:00小炒注:明日的文明,成于今日的奉獻,始于昨日的輝煌。這是一個比中國還要悠久的偉大文明。從歷史發展規律和當前伊朗事態來看,這個國家再次來到了命運的十字路口,很可能即將迎來政策大轉向.

1900/1/1 0:00:00你知道嗎 有這么一所大學,它坐落于硅谷這里產生了十余位諾貝爾獎獲得者 斯坦福大學成立于1891年,由鐵路大亨、前家利蘭·斯坦福和他的妻子簡創辦.

1900/1/1 0:00:00文/郝天 原標題《論區塊鏈原教旨主義》本文轉載自公眾號:鏈上觀 編者按 新技術探索的開端往往源于一小撮人的“烏托邦”理想,一項技術要實現普世化價值,需要推廣應用,取得理性市場認可.

1900/1/1 0:00:00英國皇后和哈里王子進行危機談判后,后者表示他不再真的想成為王室成員,并要與妻子梅根移居加拿大。我們無法證實或否認謠言,或者他的真正動機可能與計劃中的比特幣礦場的廉價水力發電、氣溫寒冷有關.

1900/1/1 0:00:00撰文:LindaXie,區塊鏈投資機構ScalarCapital聯合創始人,Coinbase早期產品經理 翻譯:盧江飛 我們每天都在消費meme,傳播meme.

1900/1/1 0:00:00